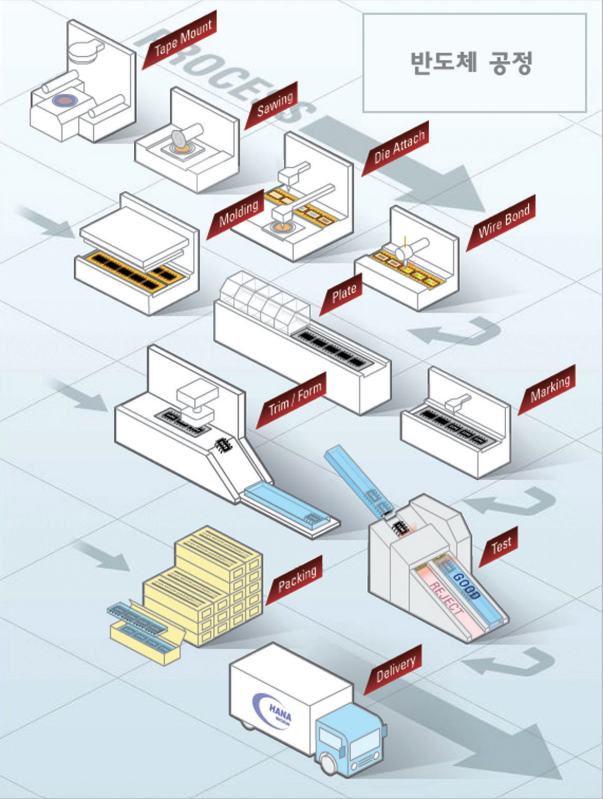

이번엔 반도체 후공정의 전반적인 과정에 대해 알아보겠습니다.

전공정에서 동그란 웨이퍼에 층을 쌓아 후공정 단으로 보냅니다. 이때부터 패키지 공정이 시작되는데요,

받은 웨이퍼의 후면을 우선 얇게 갈아 냅니다. 이것을 1) 백 그라인딩 공정 이라고 하는데요, 이렇게 웨이퍼 후면을 갈아냄으로서 PCB 와의 접촉성이나 제품화가 된 후의 CHIP 자체의 두께도 줄이기 위해 이러한 그라인딩 공정을 진행합니다.

백그라인딩 공정을 진행한 뒤에는 2) Sawing 공정 (자르는) 을 진행하여 웨이퍼를 수천 수만가지의 Die(다이) 로 쪼갭니다. 각 Die들을 PCB 나 하나의 CHIP 모듈에 들어가 설계된 기능을 수행하게 됩니다. 보통 PCB 기판에 붙히게 되는 3)Die attaching 공정을 진행하게 됩니다.

Die attaching 공정을 겉보기에는 단순히 PCB에 Die를 붙히는 작업 정도로 볼 수도 있지만, 항상 조립시 유념해야 합니다. 종종 메모리 칩을 attaching할 때 Miss 가 나기도 하는데요. 예를 들면 이렇습니다.

메모리는 8GB /16GB/32GB/64GB... 등등 메모리 용량에 따라 종류가 다양합니다. 그러나 이것이 메모리 용량에 따라 딱히 겉보기에는 크기가 구분되지 않을 때도 많은데요, 이러한 부분을 유념하여 각 PCB에 의도된 용량의 메모리 칩을 붙히는 작업이 중요합니다. 또한 chip maker 의 구분도 필요합니다. 어떠한 메모리는 삼성, 다른것은 하이닉스, 또 다른것은 마이크론 등 각각의 제조사에 따른 구분도 필요합니다. 실제로 이러한 메모리 칩 maker가 다른 것이 붙여져 추후 end customer에게 선적 되고 난 뒤 문제가 발생한 것을 뒤늦게 인지하고 complain 등을 받을 수 있습니다.

아무쪼록, attaching이 끝난 후에는 4)wire bonding 공정을 진행합니다. die와 PCB간의 전기적 연결을 하는 것이지요.이러한 본딩 방법에도 여러가지가 있는데, 이번 글에서는 이러한 전기적 연결을 하는 공정정도로 기억해 두시면 될 거 같습니다.

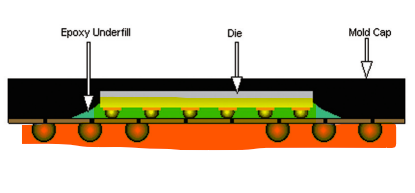

최근에는 wire bonding 외에도 Flip chip Bonding(플립칩 본딩) 이 주를 이루고 있는데요, 이는 PCB에 호환되는 범핑 패드를 만들어 놓았을 때 사용하는 방법 입니다. 즉, Die 사이즈와 PCB의 사이즈가 딱 맞게 사전에 PCB또한 미리 따로 제작을 해 두는 것이지요. Wire(선)을 사용하지 않고, ball을 부착하여 전기적 신호를 연결합니다. 참고로 오른쪽 사진의 밑에 ball 들은 PCB 와 외부를 연결하는 Ball 들 입니다. die와 pcb를 연결하는 ball 또한 왼쪽 그림처럼 내부에 있습니다.

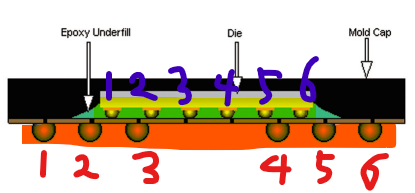

실제 mapping(맵핑)의 개념도 알아둘 필요가 있는데요, 맵핑이란 die-pcb 사이의 ball - bump 라고 합니다. 이 bump와 외부- pcb 사이의 ball 을 연결짓는 것인데요. 말로는 어렵고 아래 그림을 자세히 보고 설명드리면,

노란색 bump 와 주황색 부분의 ball 들이 연결되어 있다는 것입니다. 실제 chip을 test 한다고 하는것은 이러한 바깥의 주황색 ball ( pin 이라고도 부름) 들에 신호를 쏴서 test를 하게 되는데요, 주황색 특정 pin에 불량이 감지되었다 하면 -> 이것은 이 ball과 연결된 노란색 bump의 불량이나 fail 도 의심을 해 봐야 합니다.

즉 1~6번까지의 ball(or pin) 중 3번 핀이 fail 이 발생했다면, 이는 pin 3번과 내부적으로 연결된 bump 3 번도 문제가 있다는 뜻입니다. 해당 맵핑은 좌에서 우로 숫자를 제가 임의로 매겼지만, 실제 2차원적으로 맵핑을 하게 되면 그 순서가 달라질 수 있습니다. 즉, 가로축 세로축으로 두가지 변수를 만들어야 하는 것이지요. 예를 들면 아래 그림과 같이,

A1 -> 가장 왼쪽 윗자리 Ball을 칭하는 것입니다. 반대로 ZN(N은 임이의 숫자) 는 가장 오른쪽 아래 구석의 Ball을 칭하는 것이지요. 측 이 칩을 테스트 하고 난뒤에 만약 불량이 생긴다면, 무슨 핀인지 ex) M3 , Z3, A2 등의 핀의 위치들을 확인할 수 있으며, 이 핀에 매핑되는 bump 들 또한 칩을 파괴하여 검사하는 경우도 있는습니다. 이러한 과정을 FA (Failure Analysis)라고 합니다.

이 다음 공정부터는 다음 글에서 이어서 하도록 하겠습니다.

'반도체 및 산업이슈' 카테고리의 다른 글

| P/T RATIO 란? (시스템 OR 데이터의 안정도 측정) (0) | 2023.11.25 |

|---|---|

| OTP - Fusing 이란?(2) (0) | 2023.06.17 |

| JEDEC (반도체 표준 규격) 이란? (0) | 2023.02.13 |

| Nand vs Dram 비교 (2) | 2022.11.19 |

| RTOS 의 정의와 OTP와의 관계 (0) | 2022.09.08 |

댓글